Happy #nakeddiefriday to everyone! Let's get this ball rolling.

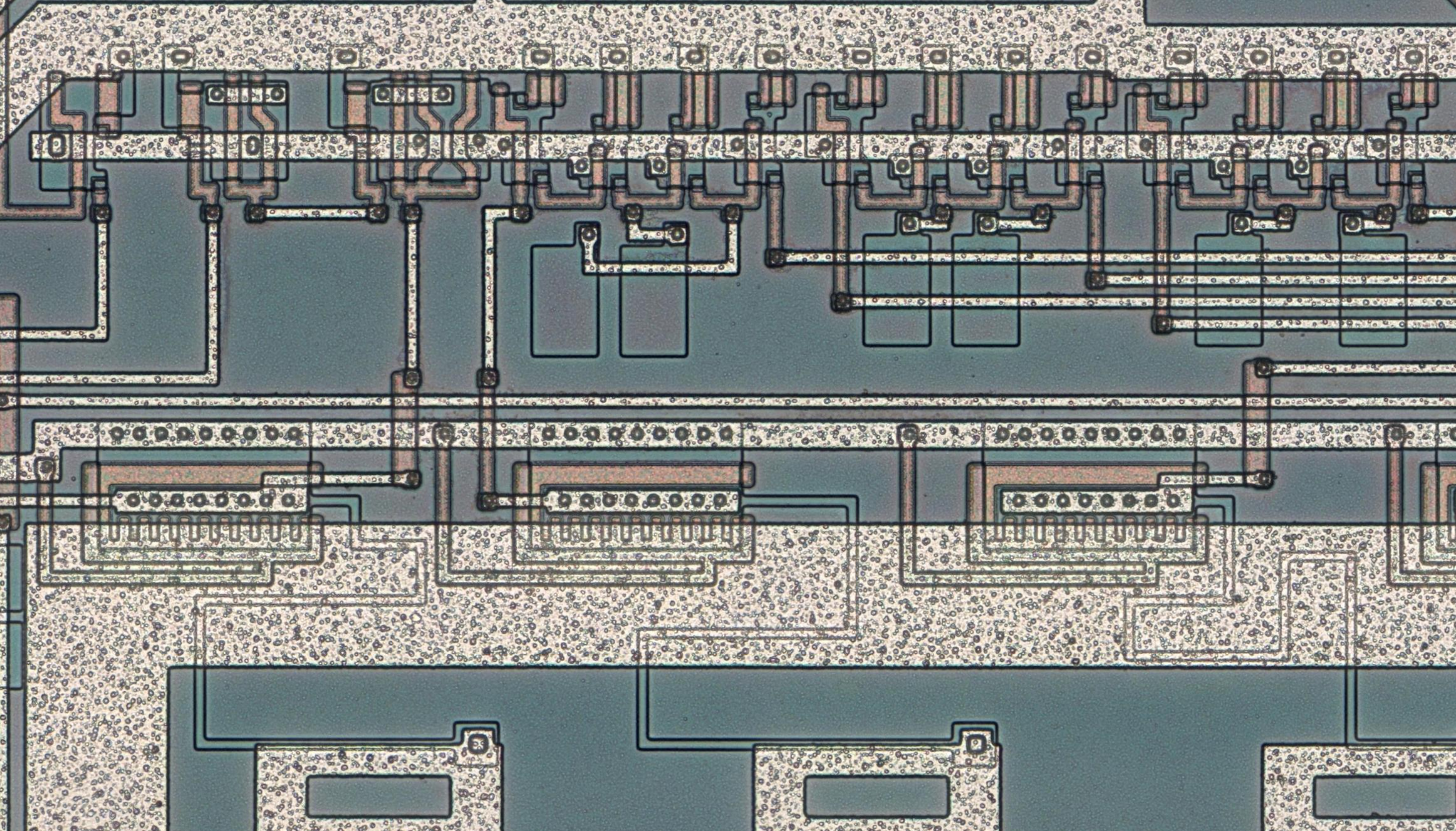

Today we have a real classic, the MC6845 by Motorola. This is a CRT controller chip used in quite a few video adapters back in the day.

Thanks to @gloriouscow for suggesting this one! We'll do a short thread looking around.

SiPron page: https://siliconprawn.org/archive/doku.php?id=infosecdj:motorola:mc6845p-jr5