@resuna @isotopp You know about Framework's commitment to upgrade motherboards? (New model drops, they sell the motherboard separately so you can buy and fit one in your old laptop—and an optional desktop cage so you can turn your old/obsolescent mobo into the brains of a set-top box or NAS or something.)

And the problem is that the alternatives are not as good (I mean user-friendly, not ethical).

Not sure if I want to venture i to the Linux jungle...;-)

@cstross 1993 here, as I recall. I had a thought earlier that the pathological lack of redesign confidence isn’t really all that different from the vestigial floppy drives and parallel ports we all loved to make fun of back in the day.

@cstross @mattgemmell As I know you (Charlie) know, the gold rush is over.

Take away the gold rush, you take away the illusion of infinite growth; the business of being the first is now the business of having the most compelling value proposition, which has terrible margins and low rates of change. (Think office chairs.)

Apple had the opportunity to say "OK, we're huge, that's a margin advantage" but it's hard to be boutique about a margin advantage. Volume specialists will pick their bones.

@cstross @mattgemmell Ah the good old days when Steve Jobs walked on water and never made a mistake.

@MikeStok @mattgemmell Oh, he made plenty of mistakes! But he buried them and moved on, and we remember him for his successes.

New Coke vibes

@cstross maybe an omen: in 2025 I bought my first non-Apple computer since 1993. @mattgemmell

@alberto_cottica May I ask what it was?

@mattgemmell a Framework 12 with Ubuntu. I decided to give repairability a chance.

@alberto_cottica Tempting machines; congrats. I don’t want to give money to US companies at the moment, though, if I can help it.

@mattgemmell just so. I looked at European alternatives but did not find any. The machine I want (sturdy, repairable, open sourced, built to last, made in Europe) does not exist, and I need to make compromises. So, I decided to put out a market signal for repairable, standardized stuff, hoping to encourage some Euro company to start a screwdriver factory based on assembling off-the-shelf components.

What I certainly get out of it is that I moved away from MacOS and into Linux.

So I am looking at Windows 11, preinstalled spyware and at the force-feeding of AI in everything.

And I see an Apple that tries to keep a product functional and mostly working despite every writer, corpocrat and stockholder demanding that Apple pisses into the product by needlessly moving the cheese, integrating AI or otherwise messing with what is the last actually usable computer (as opposed to corporate spyware and ad delivery system).

What kind of "innovation" would people like to see in a Macbook or Mac mini that would be actually useful? This is a mature product. You buy it and use it for five years, then you buy the next. And it will hopefully not have changed that much in this time, because it wasn't broken nor deficient.

What sort of innovation would I like to see in the Mac?

Look at Framework's notebook PCs and the value proposition Framework offers (unlike the rest of the PC industry)—modular and repairable.

I'd *love* a Macbook with Framework levels of repairability/configurability, even if it cost more.

@isotopp @cstross I've replaced the USB-C charging connector in my Thinkpad X395 twice this past year, requiring some guy with great eyes and hands and good skills with solder braid and flux to work on it. I too would really like more laptop makers to be like Framework, or I'm just going to flat out switch brands even if they give money to shitty people unapologetically.

That is a 233 MHZ G3 PPC with around 250 nm node size, so about 100x larger transistors than the M4 and M5, the first PPC to have an on-chip cache.

Just by clock it’s 15x times slower than a M4/M5 under full power, but it also single core. So effectively that’s easily 100x less speed by aggregated clock over all cores. It also lacks parallel (vector) instructions, so for certain modern workloads the G3 counts as an abacus.

Memory bandwidth is 0.5 GB/s vs. 155 GB/s today, so a 300x slower access in the G3.

So yes, there is innovation that has happened in the last 25 years.

Lower node size means less distance, less capacity in the connections, higher clock, less voltage, less leakage in the transistors, even higher clock possible due to that, and hence more performance.

Plus a transistor budget from 6.35 million in a G3 to 30 billion in a M4/M5: 100x smaller node size gives you 100x100 times more transistors.

All the parts in that large beige box are now in a single chip, and more.

@wordshaper @isotopp @resuna And price, don't forget the price in real terms. A Power Macintosh G3 in 1997 started at roughly $2000 (per MacTracker) before you added more RAM/storage—that was for the entry level spec. That's about $4000 today. To get there today you need a 14 core M4 Pro Mac Mini with 64Gb RAM/4Tb SSD, which is very far from the entry level—the only way to spend more is to spec with 8Tb of SSD.

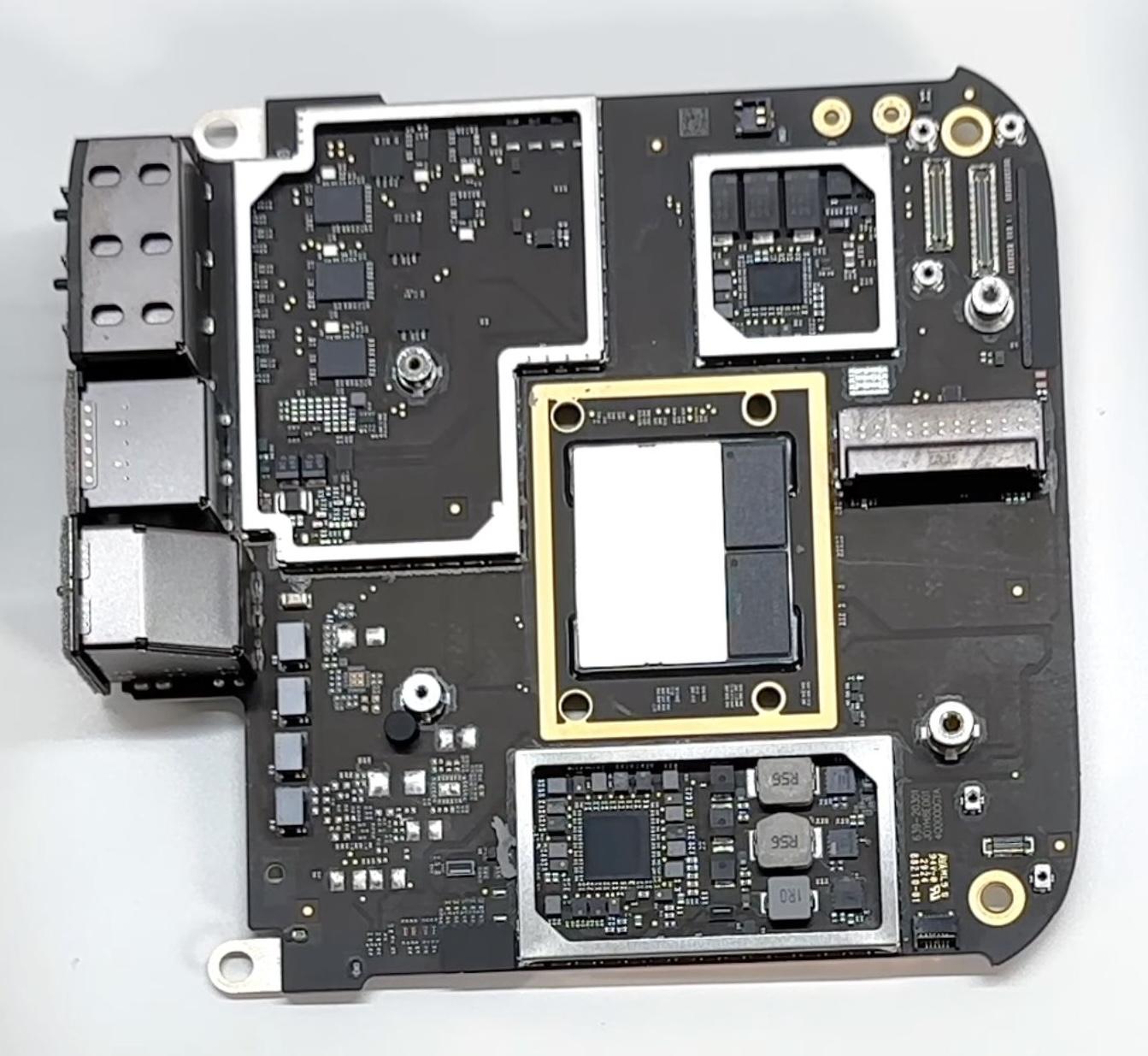

There are no parts in a Mac any more.

The system is a SoC, with memory and NVME controller on the same chip as the video and everything else. The actual flash is two additional chips right next to the CPU because they can't be integrated – yet.

The thing inside the yellow rectangle is literally the full computer – CPU, GPU, USB, Thunderbolt, Memory, NVME Controller and the two black chips are the Flash storage for the NVME.

I have not the slightest idea how anybody would make this "modular" without giving up the level of integration, the memory and flash speed and the low power consumption.

A Macbook has a few parts, but they are all HID components – touchpad, screen, keyboard, and a battery. A lot of battery.

An iPhone is basically only battery.

Image via https://vuink.com/post/znpehzbef-d-dpbz/2024/11/08/m4-mac-mini-teardown

We switched away from Macs when the line up about 6 (?) years ago was transparently lower quality in both make and power.

I've owned macs since 1988, and always justified the expense by pointing out that the computers last forever and have superior architecture and design, inside and out, and MacOS is (was) more stable.

But MacOS started to become an iOS afterthought, and their focus on "apps" and mobile computing drove their desktop stuff into the ground.